#### 2004年9月 JOURNAL OF NANI ING NORMAL UNIVERSITY(ENGINEERING AND TECHNOLOGY)

# 基于 FPGA 的连续相位 /4D QPS K 调制器和解调器

### 柯 炜.殷奎喜

(南京师范大学 物理科学与技术学院,江苏 南京 210097)

[摘要] 以 FPGA 器件为核心设计连续相位 /4DQPSK的调制器和解调器,将绝大部分功能模块由大规模 FPGA 内部资源来实现,这样既可以提高通信系统的稳定性和灵活性,又便于系统的集成化和小型化.由于连续相位 /4DQPSK调制独特的相位变化,调制器中采用了双通道设计,成功实现了过渡区相位与主要区间相位的交替产生.解调器中利用计数器控制抽样时刻,保证抽取出的信号值处于码元的主要区间.实验结果证明上述设计完全可行.

[**关键词**] 连续相位 /4DQPSK, FPGA(Field Programmable Cate Array), 调制器, 解调器 [中图分类号]TN76, [文献标识码]A, [文章编号]1672-1292-(2004)03-0041-04

/4DQPSK( /4 ——Shift Differentially Encoded Quadrature Phase Shift Keying) 调制是在 QPSK和 Offset OPSK 调制方式的基础上发展起来的一种调制 方式. 它综合了这两种调制方式的优点,降低了 QPSK信号的包络波动,既可以用相干解调又可以 进行有效地非相干解调.因而被北美和日本的数字 蜂窝移动通信系统选作标准的调制方式[1]. 尽管与 QPSK调制方式相比,/4DQPSK调制方式消除了 ± , ± /2 的相位跳变,但是该方式仍然存在着相 位跳变,信号相邻码元之间的最大相位差的绝对值 为 3 / 4. 相位跳变会增加信号的谐波分量,而谐波 分量会扩展带宽. 文献[2、3]针对 /4DOPSK调制 提出了一种改进方法,在保持码元主要部分相位不 变的前提下,在信号相邻码元之间的过渡区根据连 续化函数逐点改变相位的值,直至下一个码元的主 要部分,这样一来,在信号相邻码元之间的过渡区 内最大的相位差的绝对值趋近于零,从而既保证了 相位调制所必须的相位差别,又避免了相位改变是 阶越跳变,可以大大抑制谐波分量.计算机仿真结 果表明,在有用信息不变的情况下采用连续相位 /4DQPSK调制,带宽可以压缩约一半[3].

FPCA 器件由于具有许多突出优点,因而在许多领域中得到广泛的应用,基于 FPCA 的/4DQPSK调制器已有报道<sup>[4,5]</sup>.但这些文献主要针对普通/4DQPSK调制进行设计,本文在参考这些文献的基础上主要研究如何以 FPCA 器件为核心实现频率利用率更高的连续相位/4DQPSK调制器和解调器.

# 1 连续相位 /4DQPSK调制器

#### 1.1 连续相位 /4DQPSK调制原理

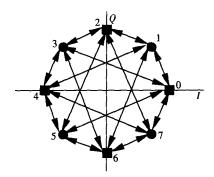

根据 /4DQPSK调制原理,相位转移如图 1 所示. 由图中可以看出,相位差 免 可以取 ± /4 或 ±3 /4,信号相邻码元之间的最大相位差的绝对值 为 3 /4. 为了减少由于相位跳变引起的谐波分量,本文在普通 /4DQPSK调制的基础上引入相位连续化技术. 连续相位 /4DQPSK调制原理可用如下公式表示:

$$I_k = \cos[\phi_k(t)] = \cos[\phi_{k-1}(t) + \phi_k(t)S(t)]$$

(1)

图 1 /4D QPSK相位转移图

$$Q_{k} = \sin[ \phi_{k}(t) ] = \sin[ \phi_{k-1}(t) + \phi_{k}(t) S(t) ]$$

(2)

其中:

$$S(t) = \begin{cases} \frac{1}{2} \left( 1 + \sin \frac{t_m}{2} \right) & | t_m | \\ 0 & \text{else} \end{cases}$$

(3)

称为连续函数,2 称为过渡区宽度,而把一个码元

收稿日期: 2004-03-15.

基金项目: 江苏省科学技术厅科研基金资助项目(2001047).

作者简介: 柯炜(1976 - ),硕士,助教,主要从事无线通信的教学和研究. E-mail:kewei @njnu.edu.cn

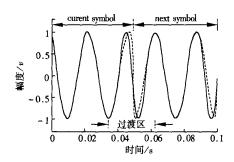

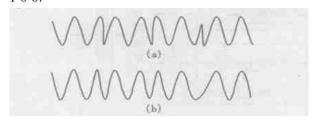

除此之外的其它部分称为该码元的主要部分. S(t) 的取值范围是[0,1],于是运用公式(1)、(2) 和(3) 正好可以使相位在过渡区 2 内完成  $\phi_k(t)$ 的变化量,即从 4,1到 4,的变化是在过渡区内逐 渐完成的,这不同于一般 /4DOPSK调制的相位跳 变,在过渡区结束后,即进入一个码元的主要部分 时相位已经达到与差分编码相对应的相位值  $\Phi_k(t)$ . 运用 Matlab 软件进行模拟,两种 /4DOPSK 调制后的典型波形如图 2 所示. 图中虚线是经非连 续相位调制后相邻两个码元的波形,从图上可以看 出,当前码元相位是 /4,下一个码元的相位为 相位跳变量为 3 /4. 实线描述的是两个相邻码元 经连续相位调制后的转移线,在过渡区结束后,即 进入每一个码元的主要区间时,相位已达到差分编 码所需的相位,所以此区间两种调制方式的波形相 同,因而图中虚线被实线覆盖.

图 2 相位连续化与非连续化时的波形比较图

#### 1.2 连续相位 /4D OPS K 调制器的 FPGA 实现

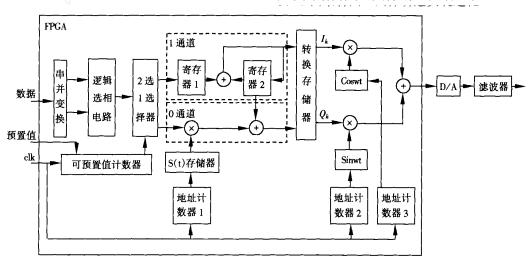

连续相位 /4DQPSK调制器的电路结构如图 3 所示. 整体上由 FPGA 器件和 D/A 器件以及滤波器 等组成. 其中 FPGA 器件实现连续相位 /4DQPSK 调制所必须的串并转换、相位选择,相位连续等功 能:D/A 器件主要把 FPGA 器件输出的数字信号转 换成模拟信号,并通过滤波放大处理以便干发送出 去.下面结合图3具体讲述实现过程.

图 3 连续相位 / 4D OPS K 调制器电路结构图

图 3 中串并转换模块将输入的数据按奇偶位 分开,变成两路并行的数据,以便干 /4DOPSK进 行相位选择,逻辑选相电路实际上是一个 4 x8 位 的存储器,其中存放 / 4DQPSK 调制可能的 4 种相 位跳变值 ± /4、±3 /4,每一个经 8 位量化,以串 并转换模块的输出值作为该存储器的地址码,来决 定逻辑选相电路的输出.接下去的二选一选择器是 为实现连续相位 /4DQPSK调制功能引入的.该选 择器的控制端与双可预置值计数器的输出端相连, 此计数器的特点是具有两个预置值,从预置值1递 减到零的过程为两个相邻码元的相位连续变化的 阶段,此时计数器输出为0,则二选一选择器开通0 通道,因此相位跳变值进入0通道,实现相位的连 续化,即相位从  $\phi_{k-1}$  开始,经过  $\phi_{k}(t) S(t)$  的作

用,由  $\phi_{k-1}$  连续变化到  $\phi_{k-1}$  +  $\phi_k(t)$  ;当预置值 1 递减到零后,意味着过渡阶段结束,此时计数器内 部由0变到预置值2.并由预置值2开始递减(直至 减到 0 再翻转回预置值 1),与此同时计数器的输 出由0翻转为1,二选一选择器开通1通道,进入正 常的 /4DOPSK的相位值,产生码元的相位主要部 分. 所以通过改变不同的预置值 1、2,就可以改变 过渡区和主要部分所占比例,产生不同的相位连续 化效果,也即过渡区宽度是可控的,这样的计数器 若用分立元件设计将十分麻烦,但利用 VHDL (Very High Speed Integrated Circuit Hardware Description Language) 语言进行设计则相当方便,既可用两个进 程分别实现两种递减计数,进程之间利用信号量建 立关联,确保当一个进程计数结束时,另一个进程 随即开始计数;也可在一个进程内部完成两种计数 功能.

0 通道实现相位的连续化功能,由存储器、乘 法器、加法器和寄存器 2 等构成, 存储器中存放的 是连续函数 S(t) 抽样后的量化值,考虑到虽然 FPGA器件的集成度越来越高,内部容量越来越大, 但片内资源毕竟有限,因而选取 S(t) 的 64 个均匀 抽样点,经8位量化后存入该存储器,实验表明该 量化精度足以满足使用需要.8位乘法器完成相位 跳变值  $\Phi_k(t)$  与 S(t) 的乘积运算. 寄存器 2 为两 个通道共用的部件,其中存放的是上一次的相位值  $\phi_{k-1}$ , 与乘法器的输出相加后即得到  $\phi_{k-1}$  +  $\Phi_k(t) S(t) . 1$  通道由两个寄存器和一个加法器构 成,其中寄存器1存放逻辑选相电路输出的相位跳 变值  $\phi_k(t)$ ,与寄存器2中存放的相位值  $\phi_{k-1}$ 相加 即得到当前相位值  $\phi_k = \phi_{k-1} + \phi_k(t)$ ,此过程紧 接在相位连续化完成后,并同时将和值转入寄存器 2中,为下一次相位连续化做准备.

转换存储器实际上由两个存储器组成,分别存放  $_{4}$  所对应的正弦和余弦值,由于连续函数  $_{5}$  (  $_{7}$  选取了  $_{64}$  个抽样点,而相位跳变值有  $_{4}$  种,所以每个存储器的容量为  $_{256}$  ×8 位,以  $_{4}$  的量化值作为地址码通过查找表的方式分别由两个支路  $_{1k}$  , $_{4k}$  输出. 这部分电路占用大量内部 RAM 资源,要求选用的 FPGA 具有足够的容量. Sinwt,Coswt 存储器中分别存放着载波的正、余弦值,根据采样定理和实验分析,把一个正、余弦波周期采样  $_{32}$  个点,经过8 位量化,恢复出来的波形足够光滑,两个支路  $_{1k}$  , $_{4k}$  分别与载波的正、余弦值相乘后,再相加即实现了连续相位  $_{44}$  风外分别与载波的正、余弦值相乘后,再相加即实现了连续相位  $_{44}$  风外公路,当然此时输出的还是数字信号,再经过  $_{44}$  次,每次有时间,这是数字信号,再经过  $_{44}$  次,是现代的证据,是是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作,是一个工作

# 2 连续相位 / 4D OPSK 解调器

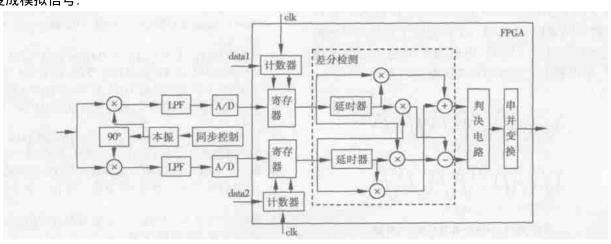

由于连续相位 /4DQPSK 调制信号仅在过渡区与普通调制信号的波形有所区别,所以连续相位/4DQPSK的解调电路与普通 /4DQPSK的解调过程基本相同,唯一不同点是增加了计数器以控制抽取模块选择码元中间部分的数据,即取到码元主要区间的数据,从而使解调时能取到正确相位.

连续相位 /4DQPSK解调器的电路结构如图 4 所示、整体上由 FPGA 器件和 A/D 器件、同步电路 以及低通滤波器等组成.其中同步电路采用锁相环 路,以保证本地振荡器的频率与输入信号的载波频 率一致,低通滤波器(LPF)用来滤去接收信号中含 有的载波二倍频项,A/D 器件将LPF处理过的模 拟信号转换成数字信号,以便 FPGA 器件处理.输 入的数据暂存在寄存器中,寄存器的输入使能端 (低电平有效)和输出使能端(高电平有效)都与计 数器的输出端相连. 计数器内部设定一个预置值 data .等于 A/D 转换器的采样频率 .但计数器的实 际计数起始值等于 data 与输入的偏移量的差,偏 移量 data1 和 data2 由 FPGA 的 I/O 口输入 .因此这 两个偏移量可根据实际情况调整. 这样做的目的是 要使提取出的信号值处于码元的主要区间,确保输 入差分检测模块的数据满足检测要求. 计数器在从 计数起始值减到 0 的过程中输出为 0.从而寄存器 的输入使能有效,所以 A/D 转换器的输出值不断 刷新寄存器内保存的值,而一旦减到0,计数器输 出翻转,由0变成1,此时输入被关闭,而输出端开 通,所要选择的数据进入差分检测模块,差分检测 模块由延时器、乘法器、减法器和加法器等组成,内 部的连接关系依据公式(4)、(5),输出量即为判决 信号  $e_k$  和  $f_k$ .

图 4 连续相位 / 4D QPS K 解调器电路结构图

$$e_k = W_k W_{k-1} + Z_k Z_{k-1} = \cos \phi_k$$

(4)

(5)

$$f_k = Z_k W_{k-1} - W_k Z_{k-1} = \sin \phi_k$$

判决电路模块实际上是两个比较器,设置参考比较电平为0电平,根据以下判决规则:

如果

$$e_k > 0$$

,则  $x_k = 1$ ;否则  $x_k = 0$  (6)

如果

$$f_k > 0$$

,则  $y_k = 1$ ;否则  $y_k = 0$  (7)

判决 输出的  $x_k$  , 经并串变换电路 恢复出

进行判决. 输出的  $x_k, y_k$  经并串变换电路,恢复出原数据流.

### 3 部分实验结果

选用XILINX公司的FPGA器件Virtex XVV3006fg456 作为目标芯片,该 FPGA 的规模是 32 万门,内部含 106 496 位 RAM,1 536 个 CLB(可配置逻辑单元). FPGA 内部功能由 VHDL 语言进行描述,VHDL 语言代码已通过 XILINX ISE 软件的仿真、综合和布局布线. 根据综合结果报告,调制器占用 2 356 个 Slice(占 76%),使用了 1 697 个 Slice 触发器(占 27%)和 3 049 个 4 输入 LUT表(占 50%). 解调器占用 2 058 个 Slice(占 66%),使用了 1 385 个 Slice 触发器(占 22%)和 2 018 个 4 输入 LUT表(占 32.5%).

调制器实验利用伪随机码发生器产生信息数 据,设置双可预置值计数器的两个预置值之比为 1:3.这样过渡区宽度占每个码元宽度的 1/4.选用 TLC7528型8位D/A转换器进行数模转换,经由 TL084 放大器构成的低通滤波器后输出已调信号. 用 TEKTRONIX2221A 型数字存储式示波器观测实 验结果,图 5b 是输出的连续相位 /4DQPSK调制 信号波形,为了便于比较,图 5a 中绘出普通 /4DQPSK调制在相同条件下的输出波形. 从图中 可以看出两种调制信号仅在相邻码元之间的过渡 区有所不同,普通 /4DQPSK调制信号存在的尖锐 跳变在连续相位 /4DQPSK中相对平缓得多,而在 过渡区结束后,进入每一个码元的主要部分时两种 调制的波形是一致的. 根据图 5 中的相位变换情 况,可以看出这段波形对应的数据信息为11010 1 0 0.

图 5 两种 /4DQPSK调制波形对比图

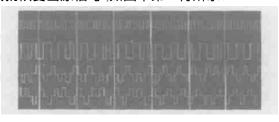

解调器中选用 MT8941 锁相环构成同步控制电路,由 MC1495 乘法器完成本振与已调信号的相乘,经低通滤波器滤去高频部分后,由 TLC549A/D 转换器把模拟信号变成数字信号,输入 FPCA 器件.图 6 是利用 XTLINX ISE 软件进行功能仿真观测到的部分解调结果,其中第 1 行信号是基准时钟信号,第 3 行和第 4 行信号是经差分检测后的 I 和 Q 两路信号,此时由于还没有经过判决电路模块,所以信号变化在(-1,+1)范围内,按照(6)、(7)式关系,判决电路将其整形成 0、1 信号,再经过并串转换就恢复出原信号,如图中第 2 行所示.

图 6 / 4D QPSK 解调器部分仿真结果

## 4 结论

随着 FPGA 技术的发展,大规模 FPGA 的容量在不断增大,价格不断下降,这使得集成复杂的算法成为可能.用它将实现连续相位 /4DQPSK调制、解调所需的大部分功能封装于其中,将有利于通信系统实现小型化和集成化,并可提高系统的稳定性.另外,由于 FPGA 器件具有可编程性,可以很方便地进行系统升级和修改,以满足不同应用场合的需要.

#### [参考文献]

- [1] 郭梯云,杨家玮,李建东. 数字移动通信(修订版)[M]. 北京:人民邮电出版社,2001.196-211.

- [2] Masahishi Kishi, Kuixi Yin. Consideration on System Capability Characteristics of Portable 2 Mbps/ 8 Mcps CDMA with Phase Continuous QPSK[C]. IEEE VTC '98. Ottawa, 1998. 924 928.

- [3] 柯炜,殷奎喜. 平滑相位的 /4DQPSK调制及其在移动通信系统中应用[J]. 电讯技术,2003,43(1):88-91.

- [4] 王永和,卜长彷. 采用 FPGA 实现 /4DQPSK 调制器 [J]. 北方交通大学学报(自然科学版),2000,24(5):53 -57.

- [5] 彭飞,赵继勇. 基于 FPGA 的全数字低中频 QPSK 调制解调器实现[J]. 电子设计应用,2003,2(9):21 23.

- [6] 侯伯亨,顾新. VHDL 硬件描述语言与数字逻辑电路设计(修订版)[M]. 西安:西安电子科技大学出版社, 1999.

- [7] 徐志军,徐光辉. CPLD/ FPCA 的开发与应用[M]. 北京:电子工业出版社,2002.

(下转第48页)

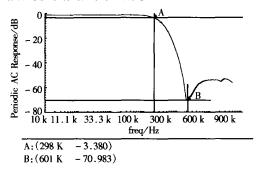

其中阻带抑制为 64 dB, 跟设计指标有一定的误差,可以通过动态范围尺度变换和阻抗尺度变换等优化方法来进一步满足设计指标,其优化后的传输函数的仿真图如图 7 所示:

图 7 优化后的六阶低通开关电容滤波器传输函数

如上所述,我们介绍了一种实现高阶开关电容 滤波器的具体方法,通过从原理出发,利用 MAT-LAB 的仿真,在 CADENCE 中实现此设计.

#### [参考文献]

- [1] Ng Wai Hon. Design of Cmos Wide-band Switched-capacitor Bandpass Filter [D]. Hongkong University of Science and Technology ,2002.

- [2] Theodore, Deliyannis, Yi Chuangsun, et al. Continues Time Active Filter Design[M]. Hongkong: Chemical Rubber Company Press, 1999.

- [3] 张志涌. MATLAB 教程 ——基于 6. X 版本[M]. 北京: 北京航空航天大学出版社,2002.

- [4] Johns D A, Martin K. Analog Integrated Circuit Design[M]. New York: Wiley and Sons Inc, 1997.

- [5] Fiex T S, Lee B, Allstot D J. CMOS Switched-current Biquadratic Filters[J]. Proc IEEE Int Symp Circuits Syst ,1990 ,71 (8):2300 2304.

# Design of Six Order Switch Capacitor Filter and Its Simulation Based on Biquard

LIN Li, LIU Yanshen

(School of Physical Science and Technology, Central China Normal University, Wuhan 430079, China)

Abstract: The principle of the switch capacitor filter was studied. The transfer of the S domain function was dealt with when the ratio of the clock frequency to the central frequency reached a certain value. The analog filter was designed by adopting the signal graph method to improve the precision and the reliability, with the function realized in the CMOS circuit of 0.25 µm.

Key words: switch capacitor, filter, MATLAB, signal flow graph

[责任编辑:严海琳]

(上接第 44 页)

# Modulator and Demodulator of Phase-continuous / 4D QPSK Based on FPGA

KE Wei, YIN Kuixi

(School of Physical Science and Technology, Nanjing Normal University, Nanjing 210097, China)

Abstract: The phase-continuous /4DQPSK modulator and demodulator, which are based on the large-scale FPGA, are introduced in this paper. The majority of the functions in the modulator and the demodulator are realized by FPGA resource, which can not only enhance the system's reliability, flexibility and integration, but also reduce its size. Because of the particular phase transformation in phase-continuous /4DQPSK, double-channel design is employed, generating transition-phase and main phase alternately. To control the sampling-time, the counter is used in the demodulator, which can ensure that the samples locate in the main phase area. The experiment results have shown that the design is feasible.

Key words: phase-continuous / 4DQPSK, FPGA, modulator, demodulator

[责任编辑:刘健]